# APPLICATIONS OF MODELLING AND SIMULATION

eISSN 2600-8084 VOL 3, NO. 1, 2019, 1-10

# Device-Circuit Level Simulation Study of Three Inputs Complex Logic Gate Designed Using Nano-MOSFETs

Ooi Chek Yee

Faculty of Information and Communication Technology, Universiti Tunku Abdul Rahman, Jalan Universiti, Bandar Barat, 31900 Kampar, Perak, Malaysia.

Corresponding author: ooicy@utar.edu.my

Received 11 January 2019, Revised 12 February 2019, Accepted 14 February 2019.

**Abstract:** Simulation study on silicon-based nano-MOSFETs logic circuits is needed to add more knowledge on the nanoscale circuit performance. Therefore, in this paper, simulation study is carried out on three inputs complex logic gate transistor circuits with four different logic families, namely (i) nano-CMOS complex gate, (ii) nano-MOSFET loaded n-type nano-MOSFET complex gate, (iii) resistive loaded 733.8  $\Omega$  nano-MOSFET complex gate, and (iv) pseudo n-type nano-MOSFET complex gate. NanoMOS is used to perform device simulation whereas WinSpice is used to perform circuit simulation. The difficulty faced during downscaling of nano-MOSFET is the realisation of low power high speed nano-MOSFET logic circuits design. Simulation output timing waveforms are used to analyse the timing characteristics of these complex logic circuits with Boolean expression  $\overline{x(y+z)}$ . Transient analysis on nano-MOSFET loaded n-type nano-MOSFET complex gate shows that theoretical modelling calculation of propagation delay and simulated propagation delay is 80% matched. With 10 nm nano-MOSFET complex logic circuits design, dynamic power reduction of 498 times and propagation delay improvement of 20 times are achieved when compared with a typical 120 nm MOSFET logic circuit.

Keywords: Complex gate; Logic family; Nano-MOSFET; Simulation; Theory.

### 1. INTRODUCTION

Downscaling of MOSFET structural dimensions from micrometer regime to nanometer regime has progressed rapidly over the last few decades [1-8]. Simulation study of 4 nm MOSFET device is available in [9]. However, this simulation used Hafnium Oxide (HfO<sub>2</sub>) as oxide material and indium gallium arsenide (InGaAs) as semiconductor material. To use the matured and fully developed Si-based process technology, 10 nm Si-based nano-MOSFET is chosen in this study [10-12]. Four different logic families, namely (i) nano-CMOS complex gate, (ii) nano-MOSFET loaded n-type nano-MOSFET complex gate, (iii) resistive loaded 733.8  $\Omega$  nano-MOSFET complex gate, and (iv) pseudo n-type nano-MOSFET complex gate with Boolean function  $\overline{x(y+z)}$  have been simulated in this paper. Circuit (i) has NMOS with a channel width, W=125 nm and a channel length, L=10 nm whereas PMOS with W=250 nm and L=10 nm in order to counter-balance the difference in electron and hole mobility. Circuit (ii) has NMOS with W=250 nm and L=10 nm whereas PMOS load with W=125 nm and L=10 nm. Circuit (iii) has NMOS with W=250 nm and L=10 nm whereas resistance load is 733.8  $\Omega$ . Circuit (iv) has NMOS with W=250 nm and U=10 nm whereas PMOS with U=10 nm whereas PMOS mander U=10 nm whereas PMOS with U=10 nm whereas PMOS ma

## 2. METHODOLOGY

Device simulation is carried out by using on-line simulator NanoMOS developed by Purdue University. Then, the CIR Spice code files for four different logic circuit families with three inputs complex logic circuits are simulated using WinSpice. The input timing diagrams and output timing diagrams are the output results of WinSpice simulation. To test the three inputs complex logic gates operations with Boolean function  $\overline{x(y+z)}$ , three inputs signals with periods of 20 ns, 40 ns and 60 ns are considered. The input signals are also used to analyse transient response including rise time, fall time, propagation delay and maximum operating frequency.

### 2.1 Theory

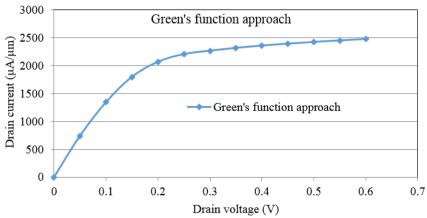

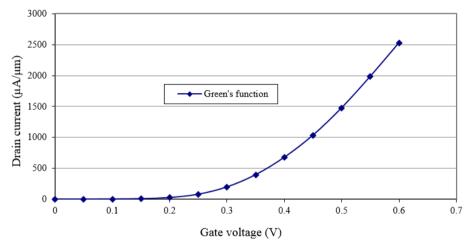

By using on-line device simulator NanoMOS, the nano-MOSFET device parameters (refer to Table 1) and current-voltage (*I-V*) graphs (refer to Figure 1 and Figure 2) are obtained which are used to calculate the timing response for nano-MOSFET

loaded nano-MOSFET complex logical circuit (refer to Table 2) [20]. The truth table for complex logical Boolean function  $\overline{x(y+z)}$  is shown in Table 3.

Table 1. Structural dimension of nano-MOSFET

| <b>Double Gate Nano-MOSFET Device Simulation Parameters</b> |                                    |  |  |

|-------------------------------------------------------------|------------------------------------|--|--|

| $V_{GS}$                                                    | 0.60 V                             |  |  |

| $V_{DS}$                                                    | 0.60 V                             |  |  |

| $V_{th}$                                                    | 0.20 V                             |  |  |

| Source/drain doping concentration $(N_D)$                   | $1 \times 10^{20} \text{ cm}^{-3}$ |  |  |

| Channel body acceptor impurity concentration $(N_A)$        | $1 \times 10^{16}  \text{cm}^{-3}$ |  |  |

| Channel width (W)                                           | 125 nm                             |  |  |

| Channel length (L)                                          | 10 nm                              |  |  |

| Source length/drain length $(L_{SD})$                       | 7.5 nm                             |  |  |

| Silicon channel thickness $(T_{Si})$                        | 1.5 nm                             |  |  |

| Top/bottom oxide insulator thickness $(T_{OX})$             | 1.5 nm                             |  |  |

| Top/bottom insulator relative dielectric constant           | 3.9                                |  |  |

| Channel body relative dielectric constant                   | 11.7                               |  |  |

| Top/bottom gate contact work function                       | 4.188 eV                           |  |  |

Table 2. Theoretical modelling calculation values of nano-MOSFET loaded nano-MOSFET complex gate

| Double Gate Nano-MOSFET Loaded Complex Gate                                |                                    |  |  |

|----------------------------------------------------------------------------|------------------------------------|--|--|

| Gate capacitance ( $C_G$ )                                                 | $5.755 \times 10^{-17} \mathrm{F}$ |  |  |

| Area capacitance ( $C_A$ )                                                 | 1.612 × 10 <sup>-19</sup> F        |  |  |

| Sidewall capacitance ( $C_{SW}$ )                                          | 6.072 × 10 <sup>-17</sup> F        |  |  |

| Total drain capacitance $(C_D)$                                            | $4.604 \times 10^{-18} \mathrm{F}$ |  |  |

| Total source capacitance $(C_S)$                                           | $1.046 \times 10^{-17} \mathrm{F}$ |  |  |

| Nano-MOSFET loaded resistance ( $R_{Load}$ )                               | 733.8 Ω                            |  |  |

| Nano-MOSFET on-state resistance $(R_{on})$                                 | 36.2 Ω                             |  |  |

| Loaded combinational gate total capacitance at output node ( $C_{total}$ ) | $1.335 \times 10^{-16} \mathrm{F}$ |  |  |

| Total capacitance between two nano-MOSFETs connection ( $C_{SD}$ )         | 1.967 × 10 <sup>-17</sup> F        |  |  |

| Rise time constant $(\tau_r)$                                              | $9.796 \times 10^{-14} \mathrm{s}$ |  |  |

| Rise time $(t_r)$                                                          | $1.314 \times 10^{-12} \text{ s}$  |  |  |

| Fall time constant $(\tau_f)$                                              | $1.803 \times 10^{-15} \text{ s}$  |  |  |

| Fall time $(t_f)$                                                          | $3.967 \times 10^{-15} \text{ s}$  |  |  |

| Propagation delay $(t_p)$                                                  | $3.457 \times 10^{-14} \text{ s}$  |  |  |

| Maximum signal frequency $(f_{max})$                                       | $7.583 \times 10^{11} \mathrm{Hz}$ |  |  |

Figure 1. Drain current – drain voltage curve of nano-MOSFET with  $V_{GS} = 0.60 \text{ V}$

Figure 2. Drain current – gate voltage curve of nano-MOSFET with  $V_{DS} = 0.60 \text{ V}$

| Inputs |   | Output |                     |

|--------|---|--------|---------------------|

| x      | у | Z      | $\overline{x(y+z)}$ |

| 0      | 0 | 0      | 1                   |

| 0      | 0 | 1      | 1                   |

| 0      | 1 | 0      | 1                   |

| 0      | 1 | 1      | 1                   |

| 1      | 0 | 0      | 1                   |

| 1      | 0 | 1      | 0                   |

| 1      | 1 | 0      | 0                   |

| 1      | 1 | 1      | 0                   |

Table 3. Truth table for complex logic gate

Equations and theories, which are used to obtain data in Table 2 are listed below. The drain current per micro width is given by

$$\frac{I_D}{W} = BC_{OX}\widetilde{v_T}(V_{GS} - V_T) \left[ \frac{1 - \frac{\mathcal{F}_{1/2}(\eta_{F1} - \frac{qV_D}{k_BT})}{\mathcal{F}_{1/2}(\eta_{F1})}}{1 + \frac{\mathcal{F}_0(\eta_{F1} - \frac{qV_D}{k_BT})}{\mathcal{F}_0(\eta_{F1})}} \right]$$

(1)

where B is the ballistic efficiency,  $C_{OX}$  is the oxide capacitance per unit area,  $\widetilde{v_T}$  is the thermal velocity and Fermi-Dirac integrals of order zero and 1/2 are used. All nano-MOSFETs, except for load transistor in nano-MOSFET loaded n-type nano-MOSFET complex gate which operated in resistive region, worked in saturation region with conditions  $V_{GS} > V_T$  and  $V_{DS} > V_{GS} - V_T$ .

$$R_{Load} = \frac{V_{th}}{I_{on-state at linear region} \times W} \tag{2}$$

Since digital logic gates operate at linear portion of *I-V* curve,

$$R_{channel\ at\ on-state} = \frac{1}{\mu_n C_{OX}(V_{DD} - V_{th})} \tag{3}$$

where  $\mu_n = 1200 \text{ cm}^2/\text{Vs}$  is the electron mobility at ballistic.

Total capacitance at output node in complex logic ( $C_{total}$ ) = Gate capacitance + Area capacitance + Sidewall capacitance + (1 × Drain capacitance) + Source capacitance

$$\tau_r = R_{Load} \times \text{Complex gate total capacitance}$$

(4)

$$t_r = 2.2 \times \tau_r \times 6.1 \tag{5}$$

It takes 6.1 times duration to pass logic 1 than logic 0 through a n-channel MOS pass transistor. The worst case fall time occurs when x ON, and y or z ON.

$$\tau_f = R_{on}C_n + 2R_{on}C_{out} \tag{7}$$

With the source capacitance,  $C_{Load}$ ,

$$C_{out} = C_{Load} + C_{Dn} =$$

Source Capacitance + Drain Capacitance (8)

$$C_n = 2C_{Dn} + C_{Sn} = (2 \times \text{Drain Capacitance}) + \text{Source Capacitance}$$

(9)

$$\tau_f = R_{on} ((2 \times \text{Drain Capacitance}) + \text{Source Capacitance}) + 2R_{on} (\text{Source Capacitance} + \text{Drain Capacitance})$$

$$= 4R_{on} (\text{Drain Capacitance}) + 3R_{on} (\text{Source Capacitance}) \tag{10}$$

$$t_f = 2.2 \times \tau_f \tag{11}$$

$$t_n = 0.35(\tau_r + \tau_f) \tag{12}$$

$$f_{max} = 1/(t_r + t_f) \tag{13}$$

The theoretical calculated value of output low voltage,  $V_{OL}$  of nano-MOSFET loaded n-type nano-MOSFET complex logic gate is given by:

$$V_{OL} = \frac{(2 \times R_{Channel\ at\ on-state})}{(2 \times R_{Channel\ at\ on-state}) + R_{Load}} \times V_{DD}$$

(14)

The equation used to obtain dynamic power is

$$P = aCfV_{DD}^2 \tag{15}$$

where a is the activity coefficient, C is the capacitance at output node, f is the frequency of switching and  $V_{DD}$  is the voltage supply [21-23].

### 3. RESULTS AND DISCUSSION

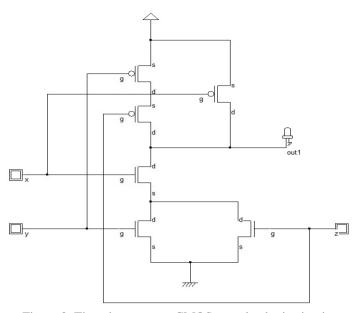

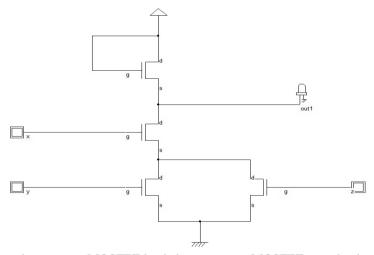

Modern nano-MOSFET devices operate between the drift-diffusion and ballistic regimes. In this paper, quasi-ballistic transport is examined. Figures 3-6 show the schematic circuits of all four logic families of complex logic circuits with Boolean function  $\overline{x(y+z)}$ .

Figure 3. Three inputs nano-CMOS complex logic circuit

Figure 4. Three inputs nano-MOSFET loaded n-type nano-MOSFET complex logic circuit

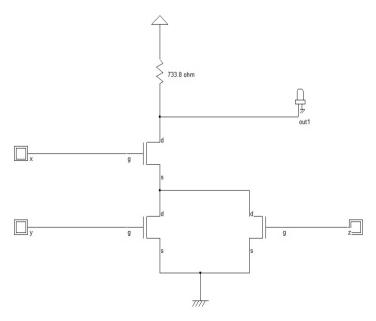

Figure 5. Three inputs resistive loaded nano-MOSFET complex logic circuit

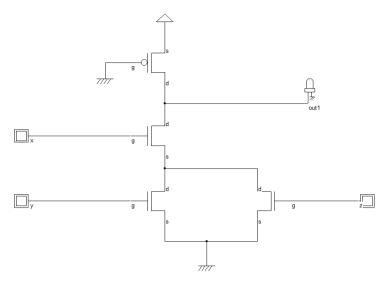

Figure 6. Three inputs pseudo n-type nano-MOSFET complex logic circuit

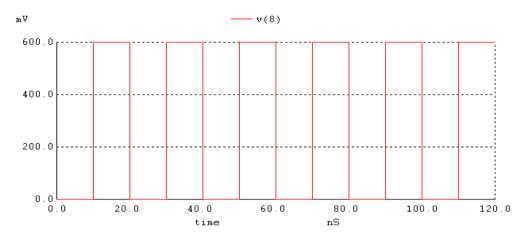

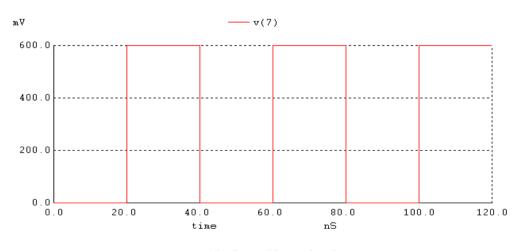

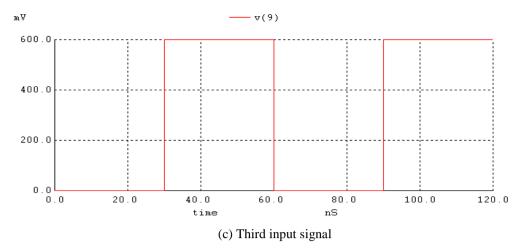

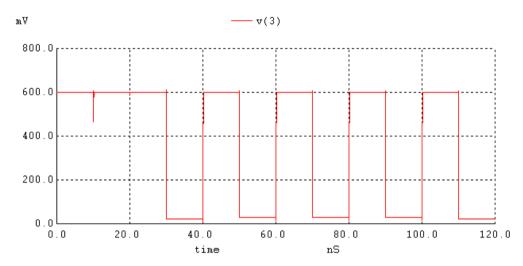

The three input signals to circuits in Figures 3-6 are shown in Figure 7. All these three input signals have 50% duty cycle and amplitude of 0.6~V.

(a) First input signal

(b) Second input signal

Figure 7. Input signals to all four complex logic circuits

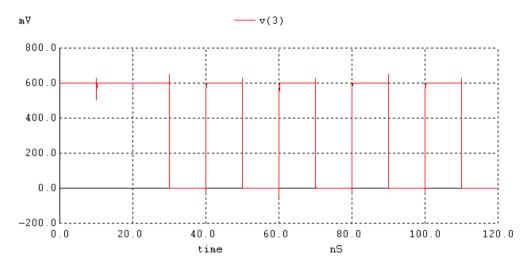

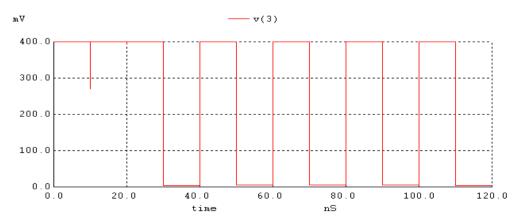

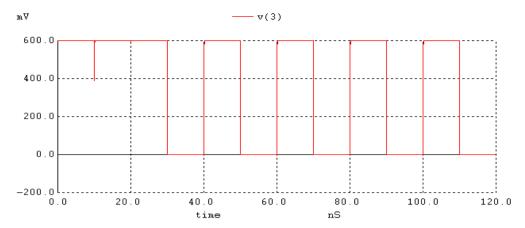

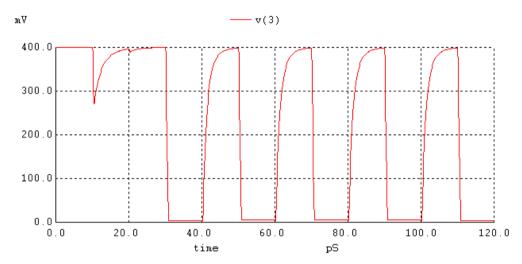

The output signals of circuits in Figure 3, Figure 4, Figure 5 and Figure 6 are shown in Figure 8, Figure 9, Figure 10 and Figure 11, respectively. These output waveforms showed correct complex logical Boolean expression  $\overline{x(y+z)}$  with inputs as in Table 3.

Figure 8. Output signal of nano-CMOS complex logic circuit

Figure 9. Output signal of nano-MOSFET loaded nano-MOSFET complex logic circuit

Figure 10. Output signal of resistive loaded nano-MOSFET complex logic circuit

Figure 11. Output signal of pseudo *n*-type nano-MOSFET complex logic circuit

Figure 9 is the output signal of logic circuit in Figure 4, with an amplitude of 0.4 V due to the threshold voltage loss of 0.2 V at the load nano-MOSFET which acts as n-type pass transistor [24-25]. The output signal of logic circuit in Figure 5 has an amplitude of 0.6 V as shown in Figure 10. The pseudo n-type nano-MOSFET logic gate has p-type nano-MOSFET with L = 10 nm and W = 125 nm whereas n-type nano-MOSFET with L = 10 nm and W = 250 nm. To reduce the output low voltage,  $V_{OL}$ , the criteria  $\left(\frac{W}{L}\right)_{n} \ge 2\left(\frac{W}{L}\right)_{Load}$  must be fulfilled. The output signal of the logic circuit in Figure 6 as shown in Figure 11, shows that the output is not 0 when compared with other output waveforms because pseudo PMOS is always ON and current still flow during output low state and thereby caused small output voltage during logic 0 state.

Figure 12 shows the transient analysis output signal for logic gate in Figure 4. Rise time and fall time are taken between 10% to 90% and 90% to 10% of output voltage signal at rising edge and falling edge, respectively. Rise time is due to charging circuit whereas fall time is due to discharging circuit. The simulated fall time is 0.692 ps and rise time is 2.69 ps with period of 120 ps which is equivalent to pulse width of 70 ps (58.33% duty cycle). The theoretical calculated propagation delay is 0.0346 ps as tabulated in Table 2, whereas the simulated propagation delay is 0.180 ps as measured from WinSpice output result. Therefore, the theoretical switching speed is 5.22 times faster than the simulated value. From Table 2 and Table 4, the theoretical maximum frequency of operation is around 758 GHz whereas the simulated maximum frequency of operation is 295 GHz, with 61% percentage error. The difference in both results occurs as quasi-ballistic transport model is used whereas in the WinSpice simulation, quantum corrected drift-diffusion model is used. Scattering events are more obvious in quantum corrected drift-diffusion model than the quasi-ballistic transport model. Therefore, the theoretical quasi-ballistic model has a shorter delay and hence a faster frequency. Thus, a high speed complex logic gate designed with nano-MOSFET has been achieved. From [11], the propagation delays of 45 nm MOSFET logic gates typically has value of 8.72 ps. When compared with the theoretical and simulated propagation delays which are 0.0346 ps and 0.180 ps, respectively as reported in this paper, complex logic gates designed by 10 nm nano-MOSFET have a faster speed. Therefore, downscaling nano-MOSFET has led to faster speed of logic circuits [10]. From Figure 12, the simulated output low voltage  $V_{OL}$  is 5 mV whereas the theoretical calculated value of  $V_{OL}$  is 53.88 mV as derived from Equation (14) in Section 2 [26]. Table 4 tabulates WinSpice simulated timing characteristic.

Table 4. Simulated value timing characteristics of three inputs complex logic gate

| WinSpice Simulation Results Using Model Level MOS6 (10% and 90% Points) |                            |                             |                            |                                         |

|-------------------------------------------------------------------------|----------------------------|-----------------------------|----------------------------|-----------------------------------------|

| Logic Gates                                                             | Rise Time $(t_r)$          | Fall Time $(t_f)$           | Propagation Delay $(t_p)$  | Maximum Operating Frequency $(f_{max})$ |

| Complex                                                                 | 2.69 x 10 <sup>-12</sup> s | 69.23 x 10 <sup>-14</sup> s | 1.80 x 10 <sup>-13</sup> s | 2.95 x 10 <sup>11</sup> Hz              |

Figure 12. Transient output signal of nano-MOSFET loaded nano-MOSFET complex logic circuit

Table 5. Power dissipation of three inputs complex logic gate

|                                | Nano-CMOS<br>Complex     | Nano-MOSFET<br>Loaded<br>Complex | Resistive<br>Loaded<br>Complex | Pseudo<br>Nano-MOSFET<br>Complex |

|--------------------------------|--------------------------|----------------------------------|--------------------------------|----------------------------------|

| Dynamic power (Watts)          | 5.827 x 10 <sup>-7</sup> | 2.826 x 10 <sup>-7</sup>         | 1.942 x 10 <sup>-7</sup>       | 3.884 x 10 <sup>-7</sup>         |

| Voltage supply (Volts)         | 0.6                      | 0.6                              | 0.6                            | 0.6                              |

| Frequency of switching (Hertz) | 5 x 10 <sup>11</sup>     | 5 x 10 <sup>11</sup>             | 5 x 10 <sup>11</sup>           | 5 x 10 <sup>11</sup>             |

Simulated fall time value is about 174 times than that of theoretical value because in simulation analysis quantum corrected drift-diffusion transport is used where scattering events cannot be ignored. Since there are many capacitance in the discharging circuit, simulated fall time are larger than theoretical fall time which used quasi-ballistic transport. Moreover, from [19], propagation delay of logic gate with  $W = 1 \mu m$ , L = 120 nm,  $T_{si} = 60 nm$  MOSFET is 3.534 ps. When compared with simulated 0.180 ps, there is an improvement of 20 times in speed in 10 nm nano-MOSFET complex logic circuits.

Table 5 tabulates the power dissipation for four different complex logic gates with Boolean expression  $\overline{x(y+z)}$  calculated using Equation (15) in Section 2 with a = 0.234375. When compared with the logic gate designed using MOSFET with W =1  $\mu$ m, L = 120 nm and  $T_{Si} = 60$  nm, which has a downscaled power dissipation of 140.9  $\mu$ W range as reported in [19], all four logic families complex gates show power reduction during downscaling of nano-MOSFET to nano-meter regime.

The power reduction for nano-CMOS, nano-MOSFET loaded, resistive loaded and pseudo nano-MOSFET complex logic circuits are 241, 498, 725 and 362, respectively when benchmarked against [19]. The nano-CMOS complex logic circuit showed the highest power dissipation because the number of switching nano-MOSFETs is the highest followed by pseudo nano-MOSFET complex logic circuit which can save two nano-MOSFETs when compared to nano-CMOS complex logic. The power dissipation of pseudo nano-MOSFET complex logic circuit is the second highest because the pseudo PMOS is always ON. The third highest power dissipation complex logic circuit is the nano-MOSFET loaded complex logic circuit because there is a small voltage drop across the load pass transistor. The lowest power dissipation complex logic circuit is the resistive loaded complex logic circuit because the load is purely resistive.

#### 4. CONCLUSION

In this paper, nano-MOSFETs have been investigated through simulation to be used in designing logical three inputs complex logic circuits with Boolean expression  $\overline{x(y+z)}$ . Besides having a correct complex logical operation as stated in the truth table, all four complex logic families circuits designed have the characteristics of low power dissipation and high speed. These low power high speed nano-MOSFET complex logic circuits are suitable in modern consumer electronics products which needs to process large amount of data quickly and have long batteries life.

#### REFERENCES

- [1] R. Hosseini and N. Teimuorzadeh, Simulation study of circuit performance of GAA silicon nanowire transistor and DG MOSFET, *Physical Review & Research International*, 3(4), 568–576, 2013.

- [2] P. A. G. Sankar and K. Udhayakumar, MOSFET-like CNFET based logic gate library for low-power application: A comparative study, *Journal of Semiconductors*, 35(7), 075001, 2014.

- [3] U. Wulf, M. Krahlisch and H. Richter, Scaling properties of ballistic nano-transistors, *Nanoscale Research Letters*, 6, 1–8, 2011

- [4] Manorama, P. Shrivastava and S. Akashe, Design and analysis of leakage current and delay for double-gate MOSFET at 45nm in CMOS technology, 7th International Conference on Intelligent Systems and Control, Coimbatore, India, 2013, pp. 301–306.

- [5] A. A. Ziabari, M. Charmi and H. R. Mashayekhi, The impact of body doping concentration on the performance of nano DG-MOSFETs: A quantum simulation, *Chinese Journal of Physics*, 51(4), 844–853, 2013.

- [6] C. Jeong, D. A. Antoniadis and M. S. Lundstrom, On backscattering and mobility in nanoscale silicon MOSFETs, *IEEE Transactions on Electron Devices*, 56(11), 2762–2769, 2009.

- [7] M. Baldo, Introduction to Nanoelectronics, MIT Open Course Ware Publication, 2011.

- [8] G. W. Hanson, Fundamentals of nanoelectronics, Pearson International Edition, 2008.

- [9] R. Chakraborty and J. K. Mandal, Design of 4 nm MOSFET and its applications, *Microsystem Technologies*, 1–8, 2018, DOI: 10.1007/s00542-018-4057-1.

- [10] K. Navi, M. Rashtian, A. Khatir, P. Keshavarzian and O. Hashemipour, High speed capacitor-inverter based carbon nanotube full adder, *Nanoscale Research Letters*, 5(5), 859–862, 2010.

- [11] M. L. P. Tan, G. Lentaris and G. AJ Amaratunga, Device and circuit-level performance of carbon nanotube field-effect transistor with benchmarking against a nano-MOSFET, *Nanoscale Research Letters*, 7, 1–10, 2012.

- [12] H. C. Chin, C. S. Lim, W. S. Wong, K. A. Danapalasingam, V. K. Arora and M. L. P. Tan, Enhanced device and circuit-level performance benchmarking of graphene nanoribbon field-effect transistor against a nano-MOSFET with interconnects, *Journal of Nanomaterials*, 2014, 1–14, 2014.

- [13] A. Verma, A. Mishra and P. Mishra, Scaling of dimensions & gate capacitances of MOSFET, *International Journal of Advanced Research in Computer Engineering & Technology*, 1(9), 272–275, 2012.

- [14] R. Gupta, B. Tutuianu and L. T. Pileggi, The elmore delay as a bound for RC trees with generalized input signals, *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 16(1), 95–104, 1997.

- [15] Y. Li and C.-H. Hwang, High-frequency characteristic fluctuations of nano-MOSFET circuit induced by random dopants, *IEEE Transactions on Microwave Theory and Techniques*, 56(12), 2726–2733, 2008.

- [16] M.-H. Han, Y. Li and C.-H. Hwang, The impact of high-frequency characteristics induced by intrinsic parameter fluctuations in nano-MOSFET device and circuit, *Microelectronics Reliability*, 50(5), 657–661, 2010.

- [17] A. A. A. Nasser, M. H. Aly, R. A. A. Rassoul and A. Khourshed, Performance of near-ballistic limit carbon nano-transistor (CNT) circuits, 21st International Conference on Computer: Theory & Applications, Alexandria, Egypt, 2011, pp. 175–182.

- [18] H. F. A. Hamed, S. Kaya and J. A. Starzyk, Use of nano-scale double-gate MOSFETs in low-power tunable current mode Analog Circuits, *Analog Integrated Circuits and Signal Processing*, 54(3), 211–217, 2008.

- [19] K. Naskar, C. J. C. Singh and S. K. Sarkar, Analytical modeling of SON MOSFET and realization inverter circuit for high speed and ultra dense low power circuits, *Journal of Nano- and Electronic Physics*, 4(2), 02023, 2012.

- [20] R. Prasher, D. Dass and R. Vaid, Performance of a double gate nanoscale MOSFET (DG-MOSFET) based on novel channel materials, *Journal of Nano- and Electronic Physics*, 5(1), 01017, 2013.

- [21] Z. Ren, Nanoscale MOSFETs: Physics, simulation and design, Ph.D. Dissertation, Purdue University, 2001.

- [22] M. Lundstrom, Notes on the Ballistic MOSFET, Network for Computational Nanotechnology, Purdue University, 2005.

- [23] R. Kim and M. Lundstrom, Notes on Fermi-Dirac Integrals, *Network for Computational Nanotechnology*, Purdue University, 2011.

- [24] O. C. Yee and L. S. King, Simulation study on the electrical performance of equilibrium thin-body double-gate nano-MOSFET, *Jurnal Teknologi*, 76(1), 87–95, 2015.

- [25] O. C. Yee and L. S. King, Simulation study of 2D electron density in primed and unprimed subband thin-body double-gate nano-MOSFET of three different thicknesses and two temperature states, *International Journal of Nanoelectronics and Materials*, 9(1), 67–84, 2016.

- [26] S. K. Sinha and S. Chaudhury, Simulation and analysis of quantum capacitance in single-gate MOSFET, double-gate MOSFET and CNTFET devices for nanometer regime, *International Conference on Communications, Devices and Intelligent Systems*, Kolkata, India, 2012, pp. 157–160.